深度学习

solidity

数据标注

自定义Toast

终端

开发板

数据可视化

激光

gerapy

函数

webshell链接

so

web3py

因果图

数据驱动

逆向分析

运动场地预约

实战教程

轮廓查找

结构生物学

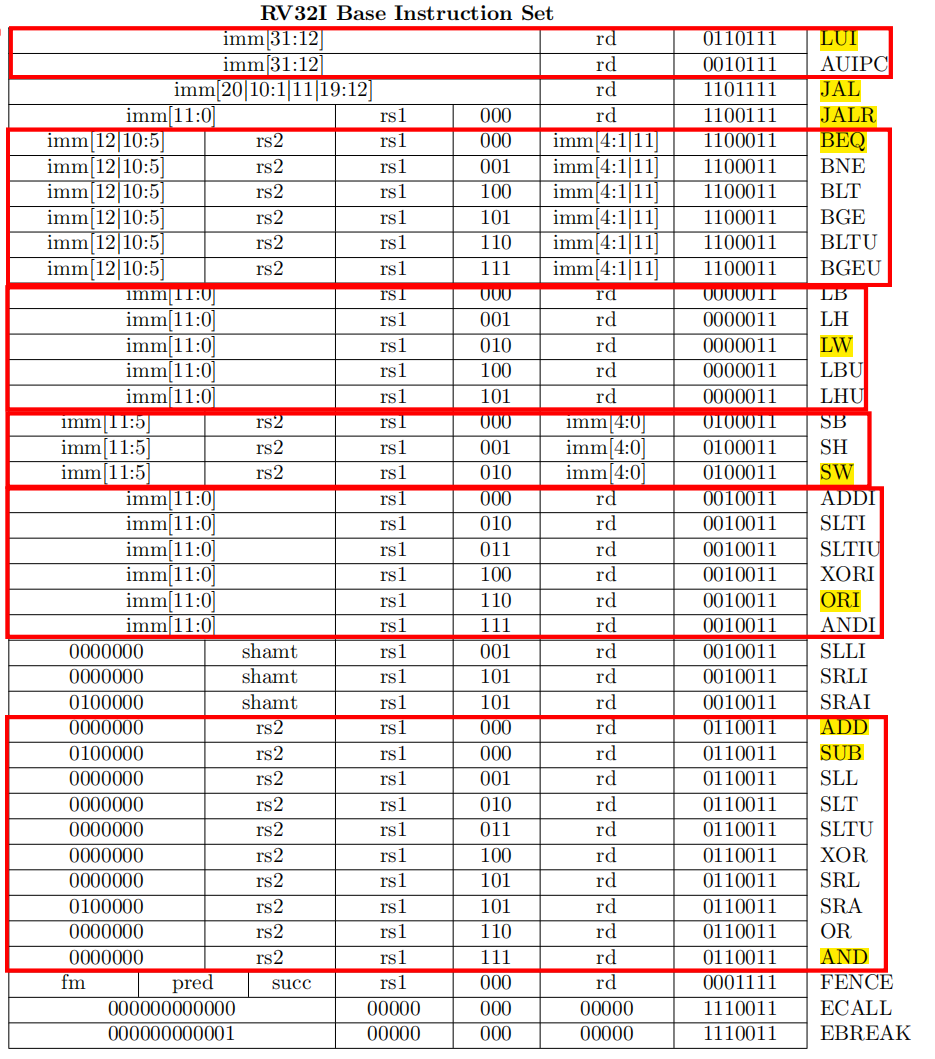

riscv

2024/4/12 12:39:43澎峰科技|邀您关注2023 RISC-V中国峰会!

峰会概览

2023 RISC-V中国峰会(RISC-V Summit China 2023)将于8月23日至25日在北京香格里拉饭店举行。本届峰会将以“RISC-V生态共建”为主题,结合当下全球新形势,把握全球新时机,呈现RISC-V全球新观点、新趋势。

本…

RISC-V公测平台发布 · 7-zip 测试

简介

7-Zip 是一个开源的压缩和解压缩工具,具有高压缩比和快速解压缩的特点。除了普通的文件压缩和解压缩功能之外,7-Zip 还提供了基准测试功能,通过压缩和解压缩大型文件来评估系统的处理能力和性能。

7-Zip 提供了一种在不同压缩级别和多…

【工具】使用asciidoctor-pdf将adoc文件转换成pdf

文章目录 配置方法配置gem镜像源安装工具 asciidoctor-pdf 将adoc转换成pdfreference 配置方法 使用gem镜像源, 安装工具 asciidoctor-pdf 配置gem镜像源

查找默认源

gem sources移除默认源

gem sources --remove https://rubygems.org/添加新镜像源

gem source…

ArchLinux搭建riscv测试环境(失败)

参考

Boot an Arch Linux RISC-V using qemu-system - JieJiSS Blog 安装ArchLinux安装所需包

sudo pacman -S arch-install-scripts git qemu-img qemu-system-riscv

sudo pacman -S riscv64-linux-gnu-gcc

安装yay

git clone https://aur.archlinux.org/yay-bin

cd yay-b…

[RISCV] 为android14添加一个新的riscv device

本篇博客将基于android-14-r18添加Sifive unmatched板子的支持。

Setup build envoronment

Establishing a build environment

$ sudo apt install git-core gnupg flex bison build-essential zip curl zlib1g-dev libc6-dev-i386 libncurses5 x11proto-core-dev libx11-de…

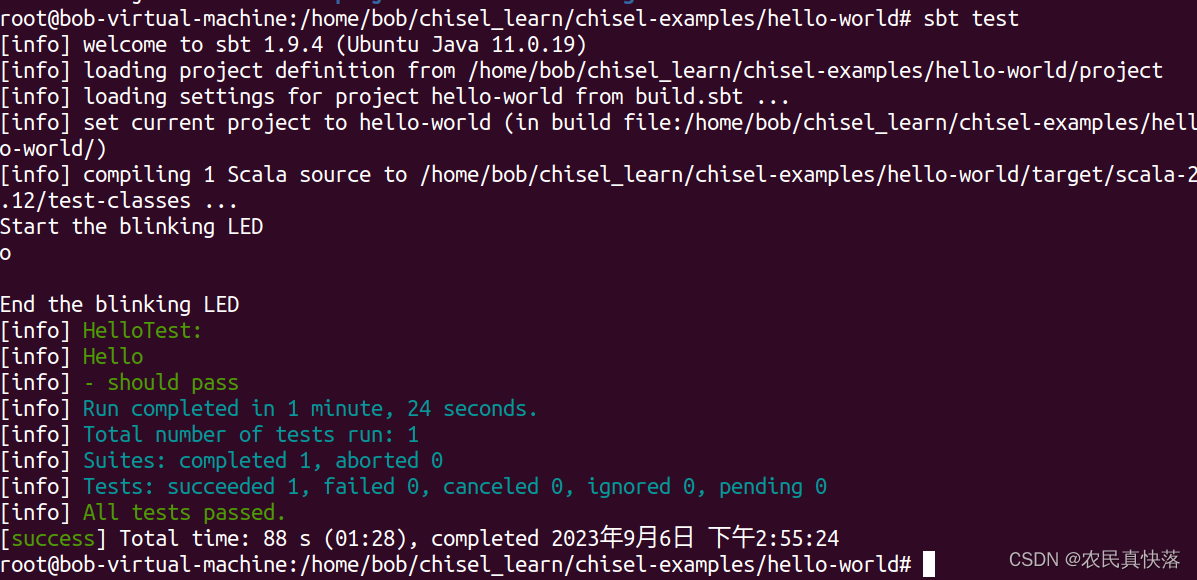

【IC设计】Chisel开发环境搭建

首先安装一个Ubuntu的虚拟机 然后给Ubuntu换个镜像,方便下载 注意换源后使用apt-get update更新下 安装vim(可以不做) 这里安装Vim是我感觉Ubuntu自带的vi编辑器似乎有问题,因为我按i进入【插入模式】并没有提示,所以…

CH32V307 开启浮点后rtthread的修改

官方版本是3.1.3,而且只有整数的,开启浮点后要做一些修改,这里问了官方并贴出来方便大家使用:

首先在mounriver开启浮点,步骤: 开启浮点:ide 开启float point->rvf, floating point abi->…

在Arch Linux上安装yay

有点麻烦。

准备

# pacman -Syu

# pacman -S --needed base-devel git

变身为普通用户

不能使用root下载代码。所以要变身为普通用户:

# sueradd tsit

# su tsit

下载代码

$ git clone https://aur.archlinux.org/yay.git

编译安装

$ cd yay

$ makepkg -si…

cpu架构之体系架构

cpu架构之体系架构

1 现代CPU体系结构简介

现代的CPU基本上归为冯诺依曼结构(也称普林斯顿结构)和哈佛结构。

1.1 冯诺依曼结构 冯诺依曼结构(von Neumann architecture),也称普林斯顿结构,是一种将程序…

RISC-V在快速发展的处理器生态系统中找到立足点

原文:RISC-V Finds Its Foothold in a Rapidly Evolving Processor Ecosystem

作者:Agam Shah

转载自:https://thenewstack.io/risc-v-finds-its-foothold-in-a-rapidly-evolving-processor-ecosystem/

以下是正文 But the open source pr…

RISC-V 借助CSR实现不修改工具链扩展指令

RISC-V 借助CSR实现不修改工具链扩展指令

通常来讲,扩展指令集是要修改工具链的,至少也要修改汇编器和反汇编器。然而借助CSR可以实现不修改工具链扩展指令集的目的。

https://blog.csdn.net/zoomdy/article/details/100176526 zoomdy at 163 dot com …

RISC-V Debug Introduction

1.JTAG简介

目前RISC-V官方支持的调试方式是JTAG(Joint Test Action Group),而ARM支持的调试方式有JTAG和SWD(Serial Wire Debug)这两种。

JTAG是一种国际标准的调试方式(IEEE1149.1),而SWD是ARM开发的。

标准JTAG采用四线方式,分别是TCK、TMS、TDI和TDO,有一个可选的TR…

RT-Thread BSP qemu-virt64-riscv 的编译环境搭建

前言 最近需要使用 RT-Thread smart 开发调试一些软件功能,由于软件功能平台无关,使用实际硬件操作,会耗费较多的时间在程序烧写环节。 打算使用 BSP qemu-virt64-aarch64 搭建一个 RT-Thread smart 的开发调试环境,可以开发验证…

RISC-V riscv64-unknown-elf 编译C文件

riscv64-unknown-elf 为 RISC-V指令集的交叉编译工具

以下环境在Liunx ubuntu x86_64 环境下进行,下面示例以生成32位文件为目标来操作使用。 screen // watch IO infos

screen /dev/ttyACM0 115200 compile riscv64-unknown-elf-gcc, RISC-V platforms riscv tool-chain…

构建 aarch64 以及 riscv64 交叉编译工具链(裸机)

构建 aarch64 以及 riscv64 交叉编译工具链(裸机)

因为我的需求是构建裸机的程序,所以我选择了裸机相关的交叉工具链

其他工具链也类似,在给出的两个官方链接中提供了所有的交叉工具链,选择合适的工具构建即可

一、…

make riscv.obj on x86: 交叉编译

0. 前言

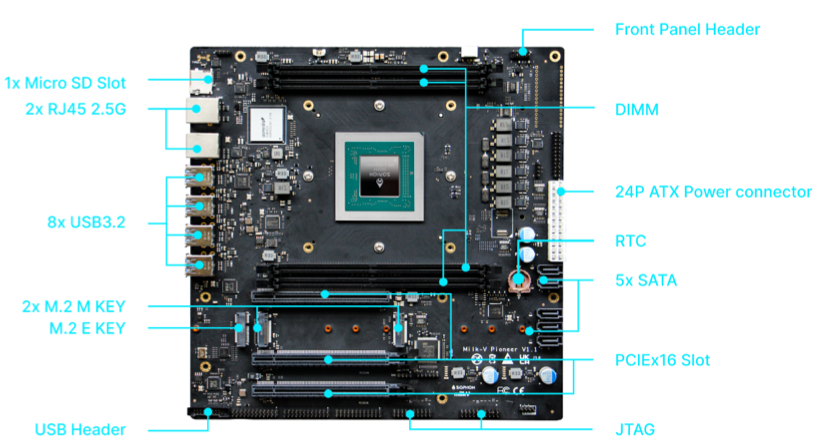

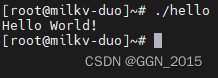

最近泰晓社区捐了几块 RISCV 的开发板给 JLULUG,作为 JLULUG 的最菜的萌新,被社团领导指派来试水。我们拿到的开发板是 MILKV-DUO,上面跑着一个几乎极简的 buzybox linux,ssh 服务端用的是 dropbear。

本文内容旨在介绍…

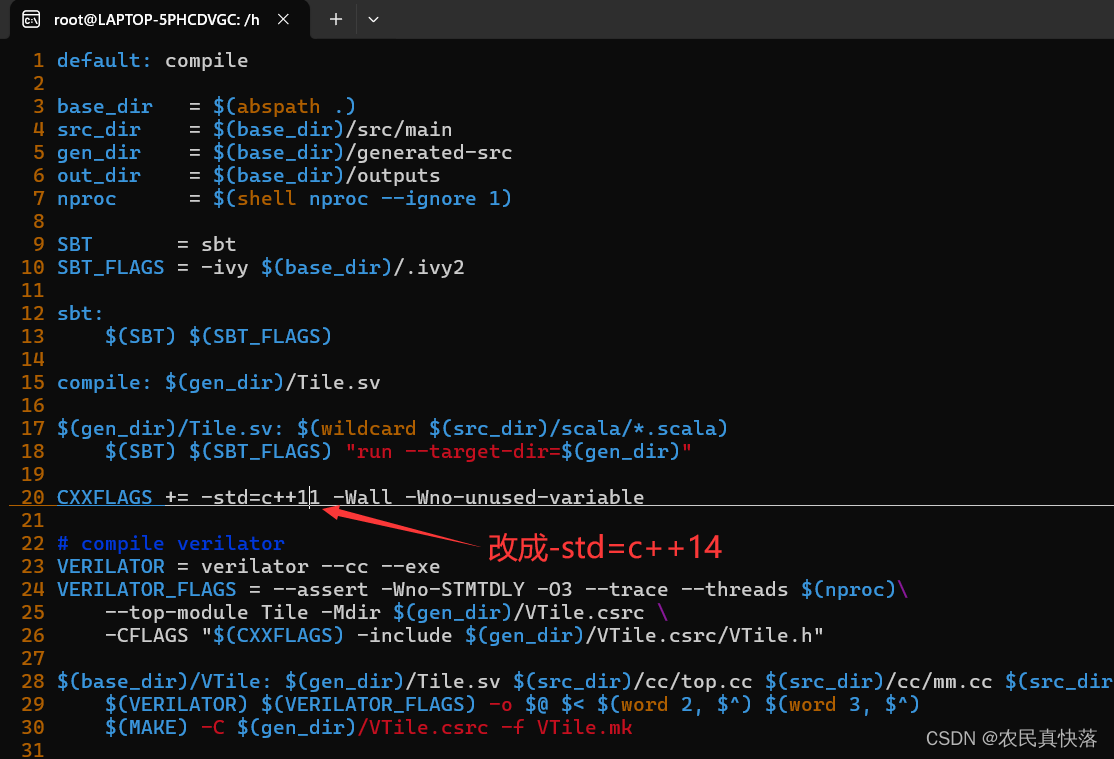

【异常处理】Verilator报错Verilator requires a C++14 or newer compiler

riscv-mini是UC Berkeley用Chisel编写的三级流水线RISC-V处理器,它实现了RV32I的用户级2.0版本ISA和机器级1.7版本ISA,是Berkeley著名的Rocket-chip项目的简化版 文章目录 环境版本:报错信息解决办法 环境版本: Verilator 5.022 U…

RISC-V体系结构的U-Boot引导过程 第一阶段

RISC-V体系结构的U-Boot引导过程 第一阶段

flyfish

.globl _start

_start:.globl使符号对链接器可见相当于C语言中的Extern,声明此变量,并且告诉链接器此变量是全局变量,外部可以访问.u-boot.lds里的ENTRY(_start)也是这里的_start。 即指定…

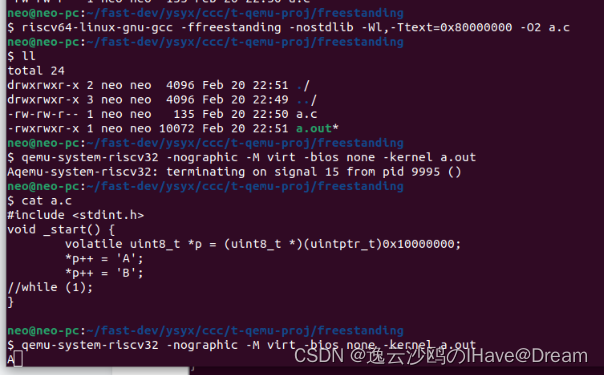

【riscv】使用qemu运行riscv裸机freestanding程序

文章目录 1. 运行显示2. 工具准备3. 裸机代码和编译3.1 源码3.2 编译 4. 使用qemu仿真运行riscv裸机程序 1. 运行显示

详见左下角, 运行时串口输出的字符 A ;

2. 工具准备

# for riscv64-linux-gnu-gcc

sudo apt-get install gcc-riscv64-linux-gnu# for qemu-s…

RISC-V Machine Mode 和 User Mode 相互切换

RISC-V Machine Mode 和 User Mode 相互切换

原文出处:https://github.com/nucleisys/Bumblebee_Core_Doc/blob/master/Bumblebee内核指令架构手册.pdf

Machine Mode 到 User Mode 的切换

在 Machine Mode 下可以直接执行 mret 指令。 Machine Mode 切换到 User …

在 RISC-V Linux 内核中添加模块

在 RISC-V Linux 内核中添加模块

flyfish

本例以添加helloworld字符设备为例

一 源码配置

1 源码

源码文件helloworld.c拷贝到 drivers/char 目录中 源码主要是输出Hello world init

2 Kconfig

打开drivers/char 目录下的Kconfig文件

在endmenu之前加上

config HELLO…

【INTEL(ALTERA)】 quartus使用Nios® V 处理器系统仿真失败,没有打印输出消息

说明

在 Synopsys* VCS* 和 VCS* MX 仿真器中模拟由以下位置生成的 Nios V 处理器系统时,可能会出现该问题: 英特尔 Quartus Prime Pro Edition 软件版本 23.1 至 23.4,或 英特尔 Quartus Prime Standard Edition 软件版本 23.1std

这是由…

在Ubuntu上搭建RiscV交叉编译环境

参考文档

安装 RISC-V 交叉编译工具链 - USTC CECS 2023

安装依赖库

sudo apt updatesudo apt -y install autoconf automake autotools-dev curl python3 python3-pip

sudo apt -y install libmpc-dev libmpfr-dev libgmp-dev gawk

sudo apt -y install build-essential bi…

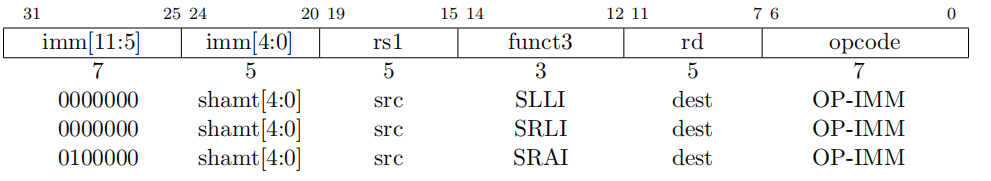

CPU设计——Triumphcore——V2版本

版本记录

指令实现情况: 【腾讯文档】Triumphcore指令实现情况

v2.1

先根据opcode确定指令格式类型,

简单分析RISCV与ARM的区别和比较

RISCV与ARM的区别和比较 文章目录 RISCV与ARM的区别和比较1、开源与专有2、指令集与实现3、性能与功耗4、生态系统与市场5、总结6、参考 RISCV和ARM都是基于RISC(精简指令集计算机)原理的指令集架构(ISA),广泛应用于各…

Qemu 启动 Linux(aarch64 与 riscv64)

Qemu 启动 Linux(aarch64 与 riscv64) 我的平台架构为 x86_64,操作系统为 Ubuntu22.04.3 这部分涉及内核的编译以及文件系统的制作 本博客中涉及了aarch64以及riscv64,以及临时文件系统以及永久文件系统,按需选择 零、…